|

在通用CPU芯片中采用DFT技术的前沿课题

可测试性设计技术(DFT)在当前集成电路设计中已经获得广泛使用,它能够提高信号的可控制性和可观察性。该技术在原有设计中插入额外的逻辑,这些逻辑在测试模式下运行并不对功能造成任何影响。如何让所有这些测试逻辑都能和谐工作,并在较少面积和较低性能开销条件下获得较高故障覆盖率,对DFT来说是两大主要问题。本文通过基于通用CPU芯片的设计,包括存储器内建自测试(BIST)、内部扫描设计、逻辑电路BIST、与IEEE Std.1149.1(JTAG)兼容的边界扫描设计,以其这些技术之间的相互关联,我们探讨了DFT技术的一些前沿课题,其中包括存储器BIST、扫描设计、逻辑BIST和BSD。这些概念已经在通用CPU芯片上得到实现且在实践中并获得了成功。

可测试性是一种设计属性,测试的基本思路是为基本输入确定特别的数值,从而根据在基本输出处得到的数值,判断内部电路是否能够正常工作[1]。可测试电路既是可以控制的,也是可以观察的。就传统而言,设计和测试流程都是相互分离的,测试只在设计流程邻近结束时才会考虑。但在当代设计流程中,测试与设计的融合时间明显提前了,产生了名为DFT的处理流程[2]。为了确保设计最大限度拥有可测试性,设计人员必须在开发流程的不同阶段运用特定的DFT技术。对不同的逻辑类型,其DFT策略也可能非常迥异,对此下文将具体加以阐述。

边界扫描

当今,绝大多数设计都从嵌入式存储器中获益,单芯片系统SoC设计就更是如此。在芯片中采用嵌入式存储器将会产生某些共同的副效应:(a)存储器可能耗费大量的设计空间并造成较高的缺陷率。(b)嵌入式存储器可能难以通过功能或其它测试类型进行高效能的测试。(c)通常的ATE可能无法对存储器进行充分测试。(d)存储器可能具备高运行速度[3]。因此,存储器测试是电路设计中非常重要的事项。幸运的是,一种名为存储器BIST的高效能方式多年来已经在存储器测试领域成功证明了其价值。因此本文将首先重点介绍有关存储器BIST的内容。

随着集成度和运行频率的提高,存储器和锁存器等存储单元得到广泛使用,导致内部扫描设计的出现,我们在此称为扫描设计,扫描设计可以通过某些商业化EDA工具来实现,比如Synopsys 公司的DFTCompiler和Mentor公司的DFTAdvisor。扫描设计的主要思路是通过测试模式下的扫描链为存储单元获得可控制性和可观察性。但对某些复杂设计来说,一些特别的DFT技术必须与扫描设计结合使用,以便取得较高故障覆盖率,比如测试点插入、时序的测试向量生成、RAM穿透处理以及宏测试技术[4,5]等,具体内容详见下文。

与存储器BIST相比,逻辑BIST正在逐渐浮出水面,它能够降低制造测试成本和系统维护成本,具备在板卡级和系统级等不同层次上开展测试的能力。它简化了诊断测试,允许开展at-speed测试。它是一种具有相当吸引力的技术,很多文章都在专门讨论这种技术。本文也简要讨论了有关逻辑BIST的一些话题。

边界扫描设计(BSD)是一种标准DFT技术[6,7],其开发目的就是补充或取代目前在高度复杂的多层电路板中采用的“针盘”测试方法,边界扫描技术已经形成了IEEE Std1149.1-1990和 IEEE Std1149.1a-1993 (JTAG)标准。在我们的项目中,边界扫描设计不仅用作互连测试,而且支持板卡级结构测试甚至功能测试,它在整块芯片测试中发挥主控器的作用。

存储器内建自测试

我们首先讨论的DFT技术问题是存储器测试,因为它可以在寄存器-传输层次的设计中完成,并且可能存在更多更大的挑战。多年来,存储器内建自测试已经成功用于解决嵌入式存储器的测试问题。存储器内建自测试简化了测试向量生成,通过基于算法产生的测试向量确保高质量的测试,显著地减少了由测试逻辑造成的时序和面积方面的不利影响。存储器内建自测试只是在存储器周围增加一层测试电路,后者则成为了其它逻辑和RAM内核之间的接口。

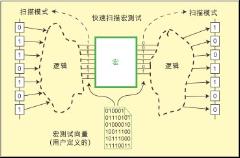

图1阐明了存储器内建自测试的原理。左侧为测试逻辑,生成测试向量,施加给带多选器的RAM,并对来自RAM的响应进行分析。右侧则是包在多选器电路中接受测试的RAM。向量生成器为实现MARCH等测试算法,并生成测试和控制信号的FSM。响应分析器则包含一个比较器或异或门压缩器,它可对照预期数据对输出数据进行比较,并确认RAM是否完好。对拥有大量RAM的设计来说,多个RAM可以通过同一个BIST控制器进行测试,这样就可以节省测试逻辑的占用面积并降低其复杂性。如果RAM容量非常大,则可采用管道逻辑技术来缩短测试时间。

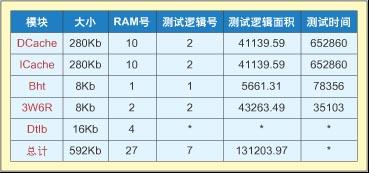

表1为我们RAM的基本信息,也是存储器BIST的结果。我们采用7个控制器在我们的CPU芯片中测试23个RAM。总面积占用低于整个芯片面积的2%。为了避免功耗问题,我们顺序测试属于同一控制器中的RAM。就Dcache、Icache和Bht等模块来说,我们使用高效能17n MARCH算法[9],该算法可以涵盖所有SAF、TF、SOF、AF、Cfin以及所有已链接Cfid、所有与CFid 或Cfin链接的TF以及与Cfids错误链接的某些CFin。

就“3w6r”模块而言,我们采用了两种特别算法。其中一种为端口交互算法,可用于检查在不同端口上短路的地址线以及检查来自某一端口的读数,且不会对任何其它读取端口造成影响。另一种算法称作唯一地址算法,可用于测试控制信号和解码电路。就多端口RAM而言,我们同样采用宏测试方法实现某些功能性测试覆盖,具体情况详见下文。

扫描设计和ATPG

扫描设计将设计分为两种运行模式,即正常运行模式和测试模式。它为电路增加一个测试模式,当电路处于这种模式时,所有存储器都在功能上形成一个或多个移位寄存器(扫描链)。这些移位寄存器链的输入和输出(也称作扫描寄存器:带多选器的DFF、带扫描时钟的DFF和LSSD)都分别连接到基本的输入和输出。这样,采用这一测试模式,所有存储器都可设定为任一想要的状态,只需将这些逻辑状态移入移位寄存器中。与此相似,通过移出扫描寄存器中的内容,可以观察存储器器的状态。

扫描设计方法可以分成三大策略:全扫描、部分扫描和分区扫描。作为一种扫描设计方法,全扫描技术用可扫描元件替换设计中所有的存储器元件,然后将其串接进入扫描链中。它是一种高效率且结果可预测的方法,拥有较高自动化流程并能够确保质量。部分扫描只取代一部分存储元件,在系统开销(时序特性和面积)与故障覆盖范围之间折中显得更加灵活。分区扫描则通常用于非常大型和复杂的设计中,通过分级分区扫描链为设计增加可控制性和可观察性。

即使采用全扫描方法,设计仍然存在多个难以控制或观察的点。我们可以在称作测试点的位置增加特别电路,向该点注入逻辑值或随时观察其状态,从而提高设计的可测试性,

扫描设计的最重大问题就是阴影逻辑的测试,这些逻辑介于RAM(或其它宏)和第1层扫描单元之间。目前有两种方法可以处理这个问题。首先是采用时序测试向量覆盖这些逻辑,这要求RAM在整个测试程序过程中做到PI可控制,从而防止破坏RAM的状态。其次是使RAM在测试模式中变得透明,将输入直接连接输出,在测试模式中绕开所有RAM,我们称之为RAM透明。但这种方法的系统开销太大。

宏测试是协助自动测试嵌入式逻辑和RAM(宏)的部件程序,它自动将用户定义的测试向量转换为扫描测试向量[10]。由于它能够协助我们在嵌入式环境中应用宏测试向量,宏测试能够在不对DUT的面积和性能造成任何不利影响的前提下提高整体IC测试质量。图2对其概念进行了说明。在宏测试的帮助下,我们芯片的扫描设计测试覆盖率超过了98%。

由于我们的芯片将以非常高的速度运行,我们不仅测试了Stuck-at和IDDQ错误,而且测试了逻辑切换和转换错误。针对这些高质量故障的测试向量可以向测试SA故障一样在ATE施加。为了达到较高错误覆盖率,降低设计的系统开销,我们在芯片的可测试性设计中采用标准的带多选器DEF扫描单元实施全扫描设计。作为整体,我们插入了38个AND类型测试点逻辑,使基本输入能够控制所有的RAM,这样我们就可以利用RAM时序向量获得较高的故障覆盖范围。宏测试技术同样可用于检查一些模块的功能,比如3w6r和Dtlb模块。

逻辑BIST

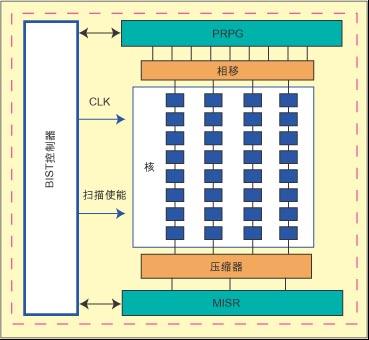

传统测试采用外部测试向量作为激励,并通过测试机将其应用于芯片。测试机检查芯片的响应,并对照作为测试向量数据的一部分保存的已知良好响应进行比较。然而,逻辑BIST在设计内实现这些工作,提供了既不牺牲测试质量又缩短测试机运行时间的方法。图3所示为逻辑BIST的原理,它主要由BIST控制器、PRPG(伪随机向量生成器)、MISR(多输入标签寄存器)和STUMPS通道(采用MISR/并行SRSG(位移寄存器顺序发生器)的自测试)等组成。逻辑BIST控制器是所有BIST逻辑的枢纽,主导内部和外部信号的交互工作。

当今有众多生成逻辑BIST向量的方法,包括ROM、LFSR、二进制计数器、蜂窝自动化等,它们通常可以分为三类:穷尽向量生成、伪穷尽向量生成和伪随机向量生成。其中,由伪随机向量生成构成的LFSR(线性反馈移位寄存器)的使用最为普遍。MISR也可用于计算来自被测试电路测试响应的标记值。通常情况下,增加移相器和压缩器有助于改善PRPG和MISR的特性。在此,全扫描目标电路的扫描链被称作STUMPS通道。

如果X传播至某观察点,那么唯一正确的标记值条件就会遭到破坏。没有初始化的RAM和不可扫描存储单元是X的主要来源。我们可以将RAM初始化,使其在测试期间处于只读状态,或采用上文所述RAM透明方法将RAM隔离。同样,我们应采用将所有存储器初始化,防止非初始化数据传播到MISR。我们应该处理透明锁存器、三态总线、TIE-X以及其它的X源。

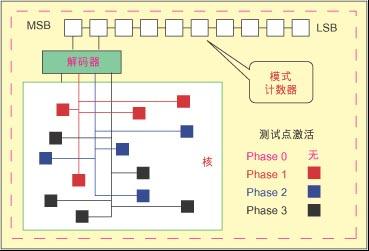

采用逻辑BIST电路,故障覆盖率通常无法达到较高的水平,因为存在等效性[11]和太多难以激励的故障。人们就这一领域的提出了众多的工作建议。测试点插入就是一种高效能和低系统开销方法,它克服了随机产生向量的阻抗(RPR)问题。如图4所示,我们可以使用一个相位解码器,使不同的测试点可以在向量计数器的不同阶段[12]被激活。概率故障仿真方法亦可用于选择最佳控制组以及有助于选择采用最少测试点最大限度改进覆盖率的观察点。

本文小结

边界扫描是一种IEEE标准协议,它不仅有益于IC和印刷电路板的互连测试,而且还提供了标准的系统测试端口和总线,使其能够将来自不同供应商的部件集成在一起。

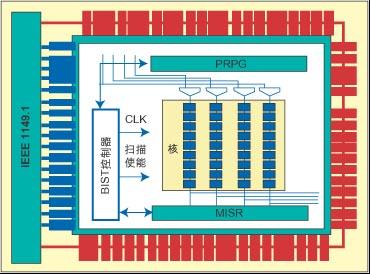

最基本的,边界扫描设计将彼此互连的边界扫描单元置于该芯片内核逻辑的周围,形成一个边界扫描寄存器。测试数据可通过一个扫描输入顺序上载至每个引脚,并通过一个扫描输出卸载。测试作业由标准测试存取端口(TAP)以及4个或5个引脚接口——TCK(测试时钟)、TDI(测试输入)、TDO(测试输出)、TMS(测试模式选择)和TRST(可选测试复位)进行控制。所有边界扫描作业都可以通过这个接口加以控制。图5所示为DFT内核和边界扫描逻辑的外部互连。除内核电源和地线之外的所有引脚都到连接边界扫描链,并受TAP控制器的控制。图5同时是BSD逻辑BIST和扫描设计的概貌,扫描设计可由板卡级和系统级TAP自由控制。

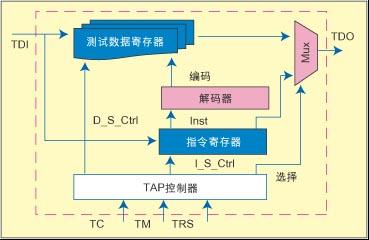

图6所示为边界扫描架构的模块示意图,它主要由5个部分组成。(1)TAP控制器是控制测试指令和数据寄存器操作的有限状态机。TAP控制器的状态取决于每个时钟脉冲(TCK)到来时TMS信号的数值。(2)指令寄存器控制边界扫描电路,它采用预定义指令集在TDI和TDO引脚之间连接特定的测试数据寄存器。(3)测试数据寄存器包括BIST以及直接连接内核的内部扫描路径。(4)指令解码器对指令进行转换以控制数据寄存器。(5)多选器模块控制数据流动的方向。

转自:互联网

|