|

SOC芯片中的DFT设计实施

1引言:

1. 1 DFT的基本概念

DFT(Design for Testability)是指在集成电路的设计过程中,通过增加逻辑、替换元件以及增加引脚等方法,解决芯片的快速、有效和自动测试问题。归纳起来,DFT实现了芯片的可测性(Testability)、可控性(Controllability)和可观测性(Observability)问题。

随着集成电路工艺水平的提高和市场需求的发展,芯片的规模也越来越大,芯片的可测性设计问题越来越突出。一方面,规模化的生产需要有效地剔除不合格芯片;另一方面,基于减少测试成本和测试周期的考虑,也推动了DFT技术的发展。近几年来讨论DFT方法和DFT工具的文章也越来越多,这说明国内更多的IC设计公司面临着规模化、产业化生产的问题。

在这样的背景下,选择一套合适的DFT软件工具,对于优化芯片的可测性设计、缩短设计开发周期以及降低规模化量产的测试成本是非常重要的。本文将通过我们的实践,向大家介绍和推荐Mentor公司的DFT软件工具。

1.2 SOC芯片的DFT策略

SOC(System on Chip)是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种I/O接口的系统级超大规模集成电路。由于SOC芯片的规模比较大、内部模块的类型以及来源多样,因此SOC芯片的DFT面临着诸多问题。

1. 存储器的测试问题

几乎每一款SOC芯片内部都集成了SRAM、FLASH、EEPROM等多种存储器,这些存储器往往由IP供应商提供。如何方便、全面、快速地测试存储器的每一个单元,是一个复杂的问题。其中包括了测试算法的确定、测试控制单元的生成、芯片级的测试控制以及并行测试等几方面问题。

2. Glue Logic的可测性设计问题

通常将SOC芯片内部除了CPU、存储器、PLL等IP之外的逻辑统称为Glue Logic。简单地说,这部分的DFT就是如何插入扫描链的问题。组成Glue Logic的模块可能是自主设计的、也可能含有IP供应商提供的IP或者wrapper。它们的设计风格多种多样,复杂程度和规模也各有不同,这就给扫描链的插入以及提高测试覆盖率增加了难度。

3. 硬IP中已有DFT与整个芯片的兼容问题

IP供应商提供的硬IP往往已经考虑了DFT的问题。在SOC总集成设计时,如何有效地利用已有的DFT,并与Glue Logic中的扫描链、存储器的BIST LOGIC兼容,是一个需要慎重考虑的问题。

4. 如何快速地自动生成测试向量及其仿真调试

大规模集成电路的DFT,包括扫描链插入、测试向量自动生成(ATPG)、以及测试向量的仿真,都是相当耗费时间的。同时,SOC芯片的设计周期往往由于市场的急迫需求被压缩的很短,留给DFT的时间就更紧张,如何快速地实现DFT、如何有效地仿真和调试、如何准确地定位存在的问题并作出修改,也是需要特别关注的问题。

2 SOC芯片DFT设计过程综述

2.1 存储器部分DFT的生成和仿真

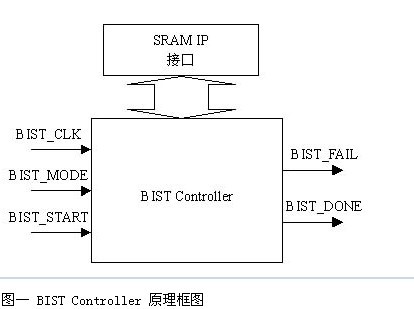

在我们设计的SOC芯片中,有一个SRAM模块,这块SRAM的接口时序和通用的SRAM类似。这部分DFT的内容,是为SRAM构建一个BIST测试机制。我们采用Mentor公司的MBISTArchitect产品自动生成了BIST控制器。仿真和芯片测试的结果表明,在芯片规模增加大约2000门的情况下,只需要100000个时钟周期就可以实现这块SRAM的测试,每个时钟周期约为40ns。并且由于加入存储器BIST而增加的管脚也很少。

下图为BIST控制器的原理框图

2.2. Glue Logic的插链、调试和仿真

在我们的SOC芯片内部,有将近20个模块共同组成了Glue Logic部分。为了降低功耗,有些模块内部有门控时钟(Gated Clock),还有些模块含有两个以上的时钟域,其中总线部分还包括一些异步逻辑,这就使得Glue Logic部分的扫描链比较复杂。在设计中我们采取以下步骤:

1. 相关网表和DFT库的准备;

2. Glue Logic的DFT预估,估计出触发器的个数,Gated Clock的模块以及Reset、CLK的情况;

3. TOP层管脚的复用设置和CLK、Reset信号及Bypass控制;

4. 采用Mentor的DFTAdvisor进行扫描链设计。这里需要考虑扫描链的长度、扫描链的个数、是否需要CLK merging(Multiple Clocks 和Multiple Clock Edges的情形)以及扫描链的均衡;

5. 为ATPG输出网表和Test procedure file。利用Mentor公司的DFT工具,能够很好地解决诸如多时钟域,异步逻辑,门控时钟等问题,从而可以达到很高的故障覆盖率。

2.3. ATPG和BIST Controller的仿真调试

MBISTArchitect为BIST controller生成了仿真激励文件,由于BIST controller 是基于BIST model而生成的,所以BIST model是否符合SRAM的接口时序,决定了BIST controller的仿真测试是否能够通过。

利用DFTAdvisor生成的test procedure文件,采用FastScan为扫描链生成测试向量。由测试向量的仿真结果,定位仿真不正确的触发器,以便及时地修改设计。值得一提的是,Mentor公司的FastScan工具在生成高覆盖率、高效率的测试向量方面,在行业享有极高的声望。

转自:互联网

|