|

VHDL语言应用指导

VHDL中的标识符可以是常数、变量、信号、端口、子程序或参数的名字。使用标识符要遵守如下法则:

・标识符由字母(A…Z;a…z)、数字和下划线字符组成。

・任何标识符必须以英文字母开头。

・末字符不能为下划线。

・不允许出现两个连续下划线。

・标识符中不区分大小写字母。

・VHDL定义的保留子或称关键字,不能用作标识符。

・VHDL中的注释由两个连续的短线(--)开始,直到行尾。

以下是非法标识符:

-Decoder —起始不能为非英文字母

3DOP —起始不能为数字

Large#number —“#”不能成为标识符的构成符号

Data__bus —不能有双下划线

Copper_ —最后字符不能为下划线

On —关键字不能用作标识符。

注:在AHDL语言中标识符要区分大小写,但在VHDL语言中不区分大小写。所以写程序时,一定要养成良好的书写习惯,应用关键字时用大写,自己定义的标识符用小写。

标识符表示的几种数据对象的详细说明如下:

1) 常数(Constant )

常数是一个固定的值,主要是为了使设计实体中的常数更容易阅读和修改。常数一被赋值就不能在改变。一般格式:

CONSTANT 常数名:数据类型:=表达式;

例:CONSTANT Vcc: REAL: =5.0;

—设计实体的电源电压指定

常数所赋得值应与定义的数据类型一致。

常量的使用范围取决于它被定义的位置。程序包中定义的常量具有最大的全局化特性,可以用在调用此程序包的所有设计实体中;设计实体中某一结构体中定义的常量只能用于此结构体;结构体中某一单元定义的常量,如一个进程中,这个常量只能用在这一进程中。

2) 变量(Variable)

变量是一个局部变量,它只能在进程语句、函数语句和进程语句结构中使用。用作局部数据存储。在仿真过程中。它不像信号那样,到了规定的仿真时间才进行赋值,变量的赋值是立即生效的。变量常用在实现某种算法的赋值语句中。

一般格式:

VARIABLE 变量名 数据类型 约束条件:=表达式;

例:VARIABLE x,y:INTEGER; —定义x,y为整数变量

VARIABLE count: INTEGER RANGE0 TO255:=10; —定义计数变量范围

变量的适用范围仅限于定义了变量的进程或子程序中。若将变量用于进程之外,必须该值赋给一个相同的类型的信号,即进程之间传递数据靠的信号。

变量赋值语句的语法格式如下:

目标变量:=表达式;

变量赋值符号是“:=”。赋值语句右方的表达式必须是一个与目标变量有相同数据类型的数值。变量不能用于硬件连线和存储元件。

3) 信号(Signal)

信号是描述硬件系统的基本数据对象,它类似于连接线,它除了没有数据流动方向说明以外,其它性质与实体的端口(Port)概念一致。变量的值可以传递给信号,而信号的值不能传递给变量。信号通常在构造体、包集合和实体中说明。信号说明格式为:

SIGNAL 信号名: 数据类型;

信号初始值的设置不是必需的,而且初始值仅在VHDL的行为仿真中有效。

1. 变量

变量只能在进程、函数和过程中使用,一旦赋值立即生效。

例:VARIABLE x, y: INTEGER;

VARIABLE count: INTEGER RANGE 0 TO 255:=10;

2. 信号

信号除了没有方向的概念以外几乎和端口概念一致。

例:SIGNAL sys_clk: BIT:=’0’;

SIGNAL ground: BIT:=’0’

在程序中,信号值输入信号时采用代入符”<=”,而不是赋值符“:=”,同时信号可以附加延时。

信号传送语句:

s1<=s2 AFTER 10ns

信号是一个全局量,可以用来进行进程之间的通信

3. 信号与变量的区别:

信号赋值可以有延迟时间,变量赋值无时间延迟;

信号除当前值外还有许多相关值,如历史信息等,变量只有当前值;

进程对信号敏感,对变量不敏感;

信号可以是多个进程的全局信号,但变量只在定义它之后的顺序域可见;

信号可以看作硬件的一根连线,但变量无此对应关系。

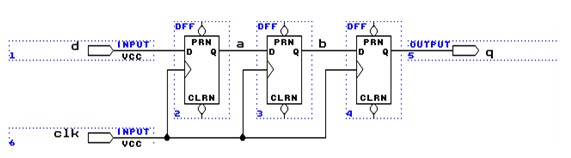

例:ENTITY reg1 IS

PORT ( d : in BIT;

clk : in BIT;

q : out BIT);

END reg1;

ARCHITECTURE reg1 OF reg1 IS

SIGNAL a, b : BIT;

BEGIN

PROCESS (clk)

BEGIN

IF clk='1' AND clk’event THEN

a <= d;

b <= a;

q <= b;

END IF;

END PROCESS;

END reg1;

ENTITY reg1 IS

PORT ( d : in BIT;

clk : in BIT;

q : out BIT);

END reg1;

ARCHITECTURE reg1 OF reg1 IS

BEGIN

PROCESS (clk)

VARIABLE a, b : BIT;

BEGIN

IF clk='1' AND clk’event THEN

a := d;

b := a;

q <= b;

END IF;

END PROCESS;

END reg1;

转自:互联网

|